Le géant taïwanais de la fonderie, TSMC, est sur le point de franchir un cap historique dans l’industrie des semi-conducteurs. À partir de 2026, TSMC prévoit de produire 60 000 wafers en 2 nm par mois, répartis sur quatre sites de production à pleine capacité.

Cette génération marque une transition technologique majeure, notamment grâce à l’adoption des transistors Gate-All-Around (GAA) et une densité de transistors encore jamais vue.

Une hausse spectaculaire du prix par wafer

Si la puissance progresse, les tarifs aussi : chaque wafer en 2 nm coûtera 30 000 dollars, soit une hausse de 50 % par rapport au prix des wafers 3 nm, facturés 20 000 dollars pièce. Cette explosion des coûts reflète à la fois la complexité technique du procédé 2 nm et la demande accrue de la part des géants de l’IA et de la mobilité.

Selon des rapports internes, les demandes de production (ou tapeouts) en 2 nm sont déjà supérieures à celles enregistrées lors des premières années des nœuds 5 nm et 3 nm.

Cela indique une adoption rapide et massive de cette technologie par les leaders du marché.

Tapeout : quand la production commence vraiment

Pour rappel, un tapeout désigne le moment où une entreprise comme Apple, Nvidia ou Qualcomm envoie le design final de sa puce à la fonderie pour démarrer la fabrication. Ces clients de TSMC, déjà bien engagés dans le développement sur le nœud de 2 nm, sont prêts à faire entrer leurs prochaines générations de puces dans la phase industrielle.

Pourquoi le 2 nm est une révolution ?

La taille du nœud de gravure (en nm) détermine directement la taille des transistors intégrés à une puce. Plus cette taille diminue, plus on peut insérer de transistors dans une même surface. Résultat : plus de puissance, moins de consommation énergétique.

Voici une comparaison de la densité de transistors (MTr/mm²) :

- TSMC 5 nm : environ 130 à 170 millions de transistors par mm²

- TSMC 3 nm : environ 190 à 220 millions par mm²

Cela signifie qu’une puce 3 nm peut contenir jusqu’à 46 % de transistors en plus qu’une puce 5 nm, ce qui se traduit concrètement par une meilleure efficacité énergétique et des performances accrues.

GAA : la nouvelle architecture transistorielle

Avec la gravure en 2 nm, TSMC introduit pour la première fois les transistors GAA (Gate-All-Around). Contrairement aux transistors FinFET actuels, le canal est entièrement entouré par la grille, ce qui réduit les fuites de courant et améliore la puissance de commutation.

C’est un changement majeur dans la conception des semi-conducteurs, car cela augmente le contrôle électrique du courant dans les transistors, une avancée essentielle pour atteindre une nouvelle échelle de miniaturisation sans sacrifier la stabilité ni la consommation.

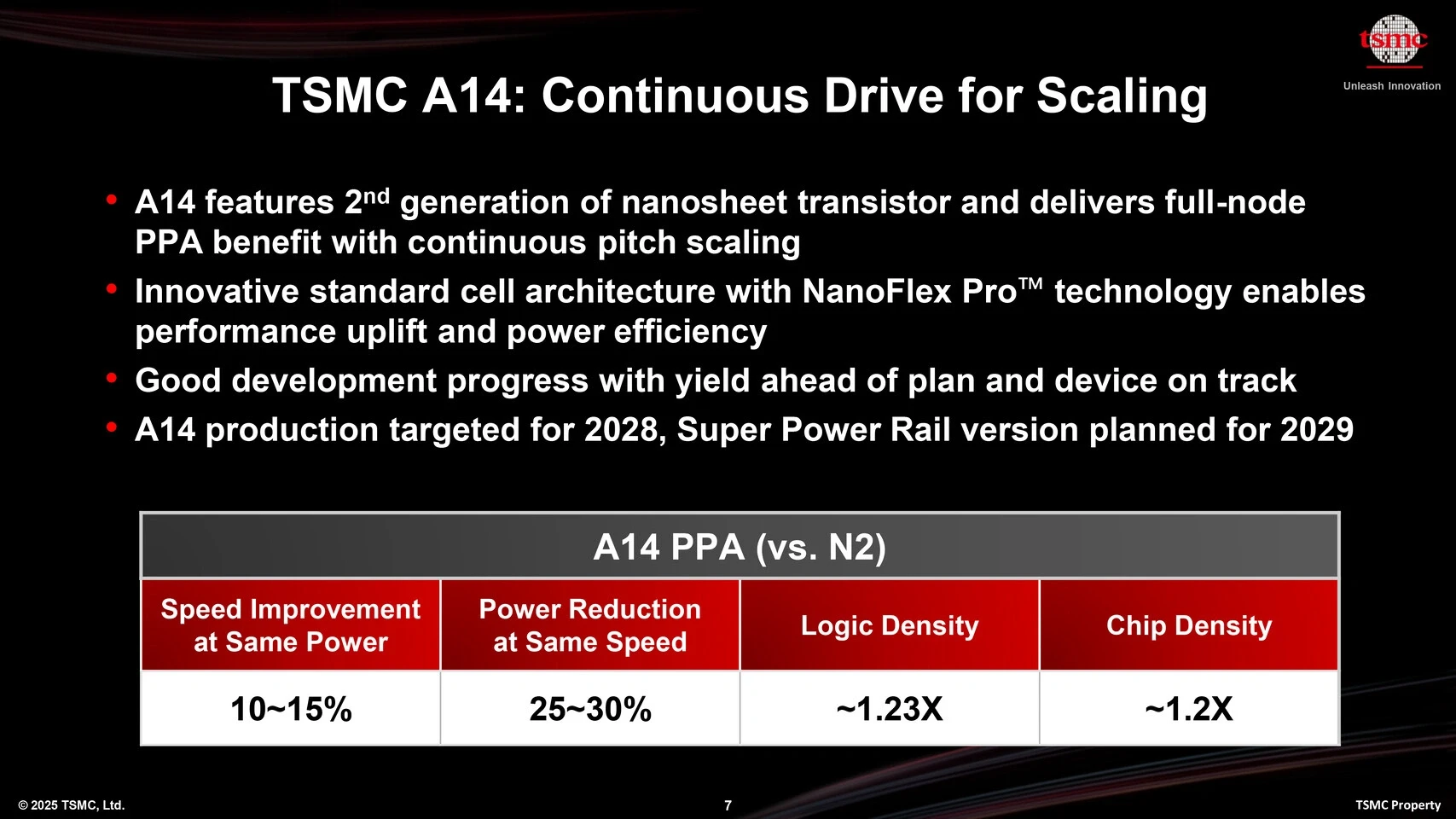

Et après le 2 nm ? Cap vers le A14…

TSMC a déjà annoncé la prochaine étape de sa feuille de route : une gravure 1.4 nm prévue pour 2028. Mais attention, le constructeur abandonnera à cette échéance la notation en nanomètres pour adopter une nouvelle unité : l’ångström (Å).

1 nanomètre équivaut à 10 Å. Ainsi, le nœud de gravure en 1,4 nm sera renommé A14 (14 ångströms). Ce changement de terminologie vise à mieux refléter les avancées atomiques du processus de fabrication, désormais à une échelle quasi moléculaire.

Que signifie cette révolution pour les smartphones ?

Avec des puces 2 nm prévues dans les smartphones haut de gamme dès 2026, la promesse est alléchante : plus d’autonomie, plus de puissance IA, moins de chauffe, et une miniaturisation accrue des composants.

Mais à 30 000 dollars le wafer, le coût final de production va forcément se répercuter en partie sur les prix des appareils. Ce qui pourrait renforcer la différenciation entre les modèles « Pro » ultra premium et les variantes plus accessibles, notamment dans la gamme Apple ou Samsung.